RAMAN: An AI Co-Processor for Edge Computing

Researchers at the Department of Electronic Systems Engineering, IISc, led by Chetan Singh Thakur, have developed an AI co-processor called RAMAN, or Re-configurable And sparse tinyML Accelerator for infereNce. RAMAN is an indigenous low-power AI co-processor designed for edge computing applications. The researchers chose to name it RAMAN as a tribute to the Nobel laureate CV Raman, the first Indian Director of IISc.

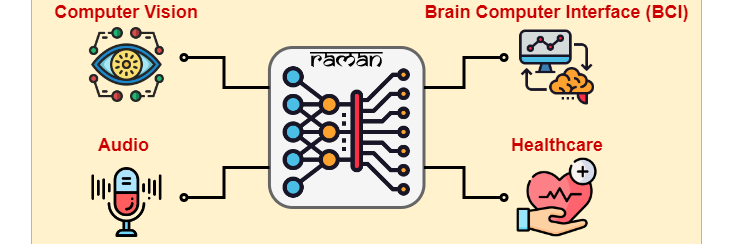

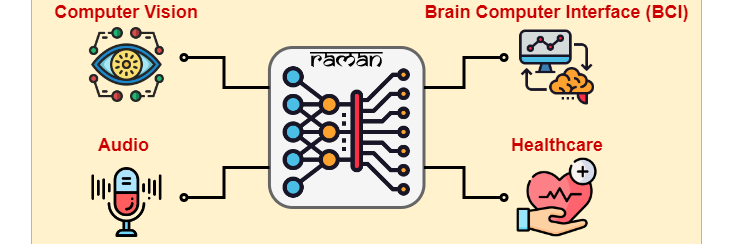

RAMAN can be configured to run ML models for various applications such as object recognition, speech identification, brain-computer interfaces, and so on. It can easily be adapted to run diverse ML models for low-power inference applications. The RAMAN accelerator is designed to leverage data and weight sparsity to deploy deep neural networks at the edge, ensuring low power consumption, minimal storage requirements, and reduced processing latency. Conducting machine learning inference directly on edge devices offers numerous advantages, including decreased latency, heightened data privacy and security, and optimised bandwidth utilisation.

RAMAN incorporates a novel dataflow inspired by Gustavson’s algorithm to reduce memory access. It supports variable precision quantisation of both weights and activations. RAMAN performs memory optimisation, such as peak activation memory reduction, by leveraging cache to reduce memory size.

RAMAN, therefore, serves as a versatile AI co-processor tailored for edge applications, capable of integration within larger Systems-on-Chips akin to ARM IPs. The researchers have demonstrated RAMAN’s various applications in vision, BCI, and acoustics.

The team includes first author Adithya Krishna, who is jointly supervised by Chetan Singh Thakur, Andre van Schaik (Director of ICNS, Sydney), and Mahesh Mehendale (TI Fellow).

REFERENCES:

Krishna A, Nudurupati SR, Chandana DG, Dwidevi P, van Schaik A, Mehendale M, Thakur CS, RAMAN: A Re-configurable and Sparse tinyML Accelerator for Inference on Edge, IEEE Internet of Things Journal (2024). https://ieeexplore.ieee.org/document/10498093

Krishna A, Ramanathan V, Yadav SS, Shah S, van Schaik A, Mehendale M, Thakur CS, A Sparsity-driven tinyML Accelerator for Decoding Hand Kinematics in Brain-Computer Interfaces, IEEE BIOCAS (2023).

Adithya K, Shankaranarayanan H, Hitesh PO, Anand C, van Schaik A, Mehendale M, Thakur CS, LIVE DEMO: TinyML Acoustic Classification using RAMAN Accelerator and Neuromorphic Cochlea, IEEE Asia Pacific Conference on Circuits and Systems (2023).

Demo: https://labs.dese.iisc.ac.in/neuronics/raman-2/

LAB WEBSITE:

https://labs.dese.iisc.ac.in/neuronics/